新奥迪A8的研发历时大约5年,在2011年就开始了定位于L3系统的研发,包括关键的激光雷达,也在2011年确定使用。

驾驶员只需在中控台上按压“人工智能按钮(AI button)”,若车辆在双向高速车道上的行驶速度低于60公里/小时(约合37.3英里/小时)行驶时,该系统将接管车辆的驾驶操作,管控车辆的启动、加速、转向及制动,奥迪虚拟座舱将提供抽象再现(abstract representation)技术 ,用抽象符号来展示新款奥迪A8的驾驶动态及周边环境。在驾驶途中,驾驶区域内的小摄像头将探查驾驶员的情况,判断其是否感到疲劳或入睡。若出现上述情况,系统将启用多级警示(multi-stage warning)功能。当车速超过60公里/小时(约合37.3英里/小时)或前方道路不再拥堵时,该系统将向驾驶员发出通知,要求驾驶员重新接管车辆的驾驶操控。若驾驶员忽视该提示信息与警示后,新款奥迪A8将缓缓减速,直至停车。

再有就是自动泊车,驾驶员可以在车外观看奥迪A8的整个停车过程。他们只需要打开智能手机中的myAudi应用,点击“奥迪人工智能”按键,就能启动相关操作。为便于监控,驾驶员需要一直按压该按钮,并通过智能手机上安装的汽车全景摄像机,查看实时视频。当停车操作完成后,该系统将自动将手自一体变速箱的档位调至P位置,停车到位后会切断发动机并熄火。当驾驶员准备驱车离开时,可通过智能手机启动奥迪A8,将车辆驶离停车位或车库。若驾驶员在车内,还可以启动中控台上的AI按钮,启用停车导航功能。在整个过程中,需要始终按压该按钮。奥迪A8在驶入车库时可实现精确转向。进入车库后,A8与墙壁或自行车等障碍物的距离非常近,若车库内部空间不足,将会中断驶入车库的操作。该功能得益于激光雷达,这也是全球第一台配备激光雷达的量产车。

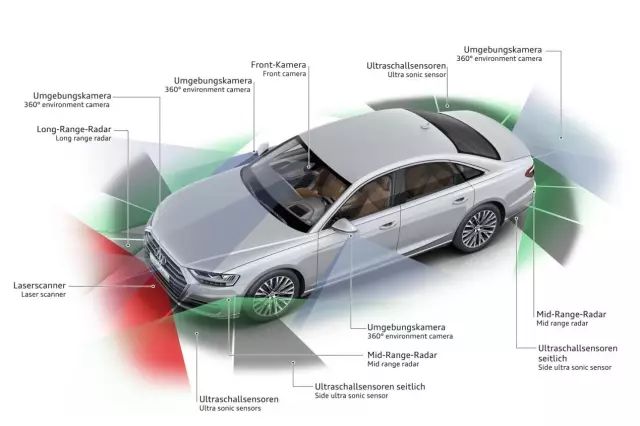

新款奥迪A8配置了一整套新款传感器,包括:在车辆前部、车侧、车辆后部配置了12个超声波传感器(可能由Valeo提供);在车辆前部、车辆后部及外部后视镜配备了4个360度全景摄像头(可能由Bosch提供),在风挡的上边缘配置了1款前置摄像头(可能由Kostal提供),在车辆的各角配置了4个中程雷达(可能由Continental提供),在车辆前部配置了1个远程雷达(可能由Bosch提供),在车辆前部配置了1个红外摄象机(infrared camera,可能由Autoliv提供),用于夜视辅助功能,在车辆前部配置了激光雷达(由Valeo提供)。

奥迪的激光雷达位于前保险杠内,该部件只有拳头大小,在数个垂直面(vertical plane)内发射光脉冲(light impluse)。通过镜面使其分布到80米(262.5英寸)的扇形区域内,其光束扇面呈现145度。近程红外线闪光的波长使得肉眼看不到这类光束,因此不会对人眼造成伤害。这个激光雷达最早由IBEO开发,后知识产权被Valeo收购,代号为Scala。原始参数如下,Valeo对Scala进行了改进,有些参数可能发生变化。

奥迪A8的ADAS系统核心为zFAS。

zFAS有4个核心元件,包括Mobileye的EyeQ3,负责交通信号识别,行人检测,碰撞报警,光线探测和车道线识别。英伟达的K1负责驾驶员状态检测,360度全景。英特尔(Altera)的Cyclone V负责目标识别融合,地图融合,自动泊车,预刹车,激光雷达传感器数据处理。英飞凌的Aurix TC297T负责监测系统运行状态,使整个系统达到ASIL-D的标准,同时还负责矩阵大灯。

Cyclone V是台积电代工的28纳米工艺的FPGA。内部架构图如下。

Altera SoC 使用宽带干线互联,HPS和FPGA架构之间的大吞吐量数据通路实现了双芯片解决方案无法提供的互联性能。架构的紧密集成支持100-Gbps的峰值带宽,实现了数据的一致性。处理器和FPGA之间没有了外部I/O通路,大幅度降低了系统功耗。在 FPGA 架构中集成了基于 ARM 的硬核处理器系统 (HPS,Cortex™-A9 MPCore),包括处理器、外设和存储器接口。它同时实现了硬核知识产权(IP) 的性能和低功耗特性,以及可编程逻辑的灵活性。

上图为Cyclone V开发板框架图。典型性能:Cyclone V SX SoC - 925 MHz, 110K LE

• 2 GB DDR3 SDRAM (1 GB processor and 1 GB FPGA)

• Ethernet, USB 2.0 On-The-Go (OTG), CAN, I2C,and UART interfaces

• Integrated Intel FPGA Download Cable II circuitry

• PCIe (rootport and endpoint support)

• Power supply and all cables

• Boots Linux on power up

值得一提是FPGA支持的总线并非普通意义的以太网或者说车载以太网,而是由瑞萨、TTTech主导的deterministic 以太网又叫实时以太网或时间触发以太网,也就是下一代车载总线网络标准TSN的雏形。TSN源自航空业的需求,由AFDX升级而来,随着无人驾驶的来临,汽车工业对车内总线的需求变得与飞机越来越接近,要求高度可靠,能够容忍系统延迟,抖动,容错,1Gb/S的带宽。可以容纳数百个传感器,甚至上千个。TTTech早先主要为飞机开发电子架构系统,进而延伸至汽车领域。zFAS里的deterministic 以太网包含了三种标准,包括SAE AS6802,就是TSN的雏形,用在大型飞机上。还有传统的IEEE802.3标准,IEEE802.1QAVB标准。兼顾高可靠性与低成本。

TTTech开发了平台中间件,允许在平台上运行多个虚拟机,且保证安全可靠。中间件兼容Autosar。顺便说一句,三星自动驾驶基金的第一项投资就是投资TTTech,投资额近9000万美元,这家奥地利公司非常优秀。

ASIL,是ISO 26262标准中的重要评价体系,用于识别系统危害并对危害风险等级进行评估。AISL分为四个等级,分别为A、B、C、D,其中A是最低等级,D是最高等级。众所周知,很多芯片只能达到A级或B级,有些连A级都达不到。有两种解决方式,一种就是添加一套甚至两套一模一样的冗余系统,成本不可避免地大幅度增加了,另外一种就是采用达到ASIL-D级的MCU,采用类似容错服务器的方法来提升系统的安全性,英飞凌的TC系列MCU是首选,也几乎是唯一选择,英伟达的DrivePX2也是如此。英飞凌的TriCore内核,是使英伟达解决方案能够达到D级标准的重要组成部分。zFAS也是如此。下图为TC297T的内部框架图。

TC297t包括三颗独立的TriCore 32位内核,一颗主核,两颗校验核,三颗即可工作在Lockstep状态。Lockstep是在电脑和云计算领域大量使用的技术,简单的说,OCKSTEP技术使用相同的、冗余的硬件组件在同一时间内处理相同的指令。LOCKSTEP技术可以保持多个CPU、内存精确的同步,在正确的相同时钟周期内执行相同的指令。该技术保证能够发现任何错误,即使短暂的错误,系统也能在不间断处理和不损失数据的情况下恢复正常运行。

我们知道系统BUG是很难被彻底完全发现的,程序员最痛苦的一种bug就叫海森堡bug,有阅历的程序员都遇到过这种情况:有个bug让程序崩溃了,但当程序重启后,这个bug消失了。不论你用多少的时间和精力来试图让bug重现,bug就是人间蒸发了。这样的bug被称为海森堡bug,在某一个给定的时间点,一个电子所处的位置是无法确定的,也无法跟踪它的轨迹。同理当你去debug、探测、隔离一个bug时,你的这些动作会导致bug改变它们的行为表现,这些bug就叫做海森堡bug (Heisenbugs)。这种事情是有可能的,比如,如果你使用未初始化的变量,这会导致一个bug出现。然而,当你试图debug这个程序时,程序却没有任何异常,因为很多的debug工具会自动初始化变量为0,所以这些bug将不会再现。TC297T就可以解决这种bug。

下一篇我们将分析特斯拉的计算平台。